在電子工程的宏大世界中,電路板貼圖(PCB Layout)常常是隱藏于光鮮產品外殼之下的幕后英雄。它不僅是功能實現的物理載體,更是一門融合了嚴謹工程學與微觀布局藝術的學問。一張優秀的電路板貼圖,是電子設備穩定、高效運行的無名基石。

一、何謂電路板貼圖?

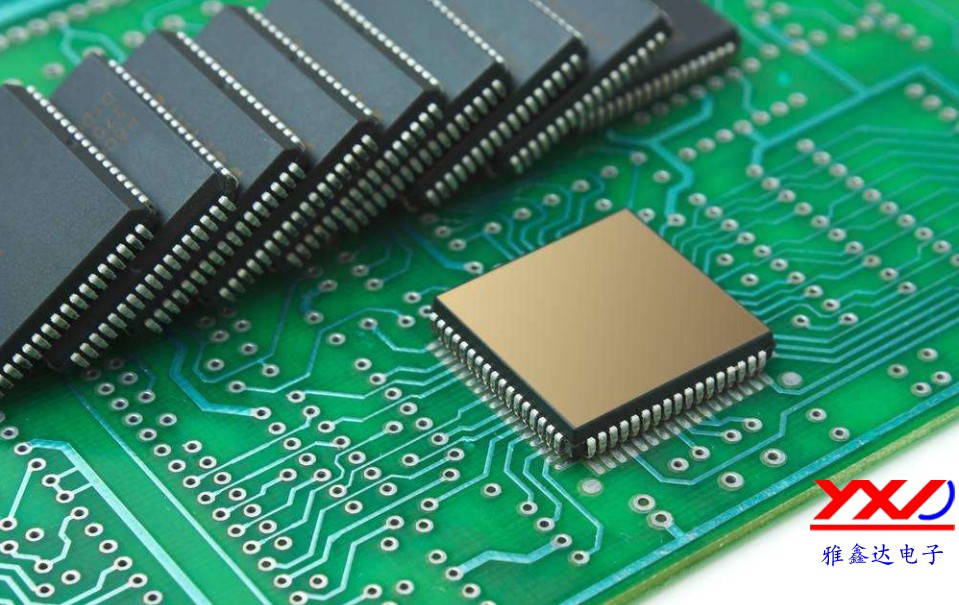

電路板貼圖,通常指印刷電路板(PCB)的設計布局圖。它是將抽象的電路原理圖,通過專用設計軟件(如Altium Designer, Cadence Allegro, KiCad等),轉化為具體的、可用于生產的物理連接圖。這個過程決定了成千上萬的電子元器件(電阻、電容、芯片、連接器等)在板卡上的精確位置,以及連接它們的銅箔走線(Trace)的路徑、寬度和層疊關系。貼圖的質量直接關系到電路的信號完整性、電源完整性、電磁兼容性、散熱性能以及最終的生產成本與良率。

二、貼圖的藝術:從功能到美學的平衡

- 功能優先的邏輯布局:貼圖的首要任務是實現電氣功能。工程師需要遵循嚴格的電氣規則,例如高速信號線的等長處理、阻抗匹配、敏感信號的屏蔽、大電流路徑的加寬、模擬與數字區域的隔離等。元器件的布局需考慮信號流向的順暢,減少不必要的交叉和回流路徑。

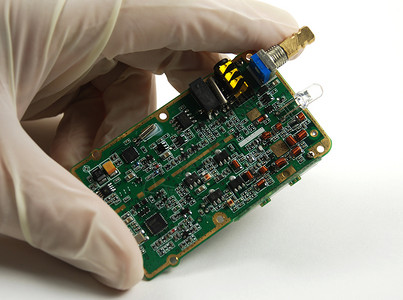

- 空間利用的微觀藝術:在有限(且昂貴)的板卡面積內,如何優雅地“排兵布陣”,是貼圖工程師的核心技能。這涉及到對元器件封裝尺寸的精確掌握、走線通道的巧妙規劃,以及過孔(Via)的合理使用。優秀的貼圖往往在滿足所有電氣和機械要求的前提下,呈現出一種緊湊、有序、甚至富有韻律感的視覺美感,堪稱“硅基板上的微雕藝術”。

- 多層設計的立體迷宮:現代高密度電子設備普遍采用多層板(四層、六層、八層甚至更多)。貼圖工程師需要在垂直空間上進行規劃,分配電源層、接地層和信號層。不同層間的走線需避免相互干擾,并通過過孔實現立體連接,這如同在三維迷宮中規劃最優路徑,極具挑戰性。

三、貼圖背后的工程智慧

- 信號完整性(SI)與電源完整性(PI):高頻數字電路和高速接口(如USB 3.0, PCIe, DDR內存)對信號質量要求極高。貼圖需控制走線的特征阻抗,減少反射、串擾和衰減。為芯片提供穩定、干凈的電源供應同樣關鍵,這需要精心設計電源分配網絡(PDN),包括去耦電容的布置和電源平面的分割。

- 電磁兼容性(EMC)設計:糟糕的貼圖是電磁干擾(EMI)的主要來源。通過合理的布局、接地設計和屏蔽手段,將電路板的電磁輻射控制在標準以內,并增強其抗外部干擾的能力,是貼圖必須考慮的環節。

- 可制造性設計(DFM)與可測試性設計(DFT):貼圖不能只存在于電腦屏幕,最終要走向生產線。設計必須符合PCB制造廠的工藝能力(如最小線寬線距、孔徑),并考慮元器件焊接(如SMT貼片)的便利性。需要預留測試點,方便后續生產測試和故障診斷。

- 熱管理:功率器件會產生熱量。貼圖時需考慮散熱路徑,如將發熱元件靠近板邊或散熱器,在底層鋪設散熱焊盤和過孔陣列,利用銅箔和內部層進行導熱。

四、從藍圖到現實:貼圖的流程

一個完整的PCB貼圖流程通常包括:

- 前期準備:確認原理圖、元器件庫、結構尺寸、安裝孔位、接口位置等。

- 規則設置:根據電路特性和工藝要求,在設計軟件中設定所有電氣和物理約束規則。

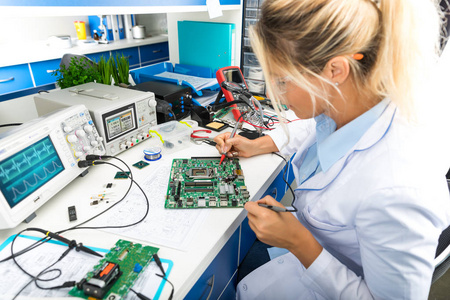

- 元器件布局:進行初步和詳細布局,這是最關鍵也是最考驗經驗的一步。

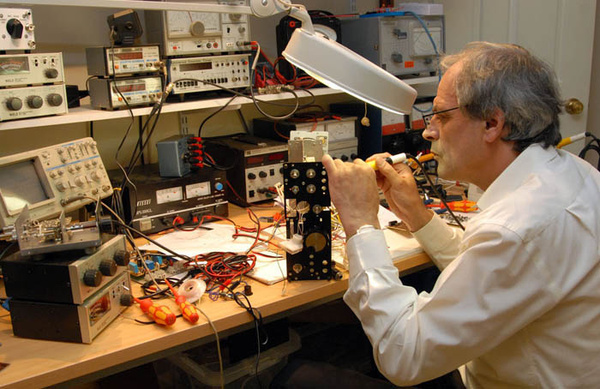

- 布線:手動、自動或兩者結合完成所有電氣連接。高速關鍵網絡通常需要工程師手動精心布線。

- 設計驗證:使用DRC(設計規則檢查)和電氣規則檢查工具,確保設計無誤。可能進行信號完整性仿真。

- 輸出生產文件:生成Gerber文件(光繪文件)、鉆孔文件、裝配圖等,交付給PCB工廠和貼片廠。

###

電路板貼圖,這張看似冰冷而復雜的線條與幾何圖形集合,實則凝聚了電子工程師對電流與信號的深刻理解,對空間與秩序的極致追求,以及對功能與可靠性的莊嚴承諾。它是連接抽象思想與物理世界的橋梁,是每一臺智能設備跳動的心臟與神經網絡。在電子工程不斷向更小、更快、更集成方向邁進的今天,電路板貼圖技術的重要性愈發凸顯,它將繼續作為核心技術,驅動著整個信息時代的硬件創新。下一次當你手持精密的電子設備時,不妨想象一下,在其內部,正靜默運轉著一幅由智慧繪就的、復雜而精美的微觀城市地圖。